Компания AMD недавно получила патент №US20260003794A1 на технологию, которая предусматривает использование многослойной структуры для второго уровня кэш-памяти. Данная технология позволит значительно повысить производительность процессоров за счёт увеличения объёма и уменьшения задержки при обращении к L2-кэшированию.

Ранее AMD уже успешно применила аналогичный подход в производстве третьего уровня кэш-памяти под названием «3D V-Cache» для линейки процессоров Ryzen X3D. Теперь же инженеры компании намерены расширить границы использования этой технологии и создать аналогичную конструкцию для второго уровня кэширования, что, в свою очередь, ещё больше увеличит вычислительную мощность процессоров.

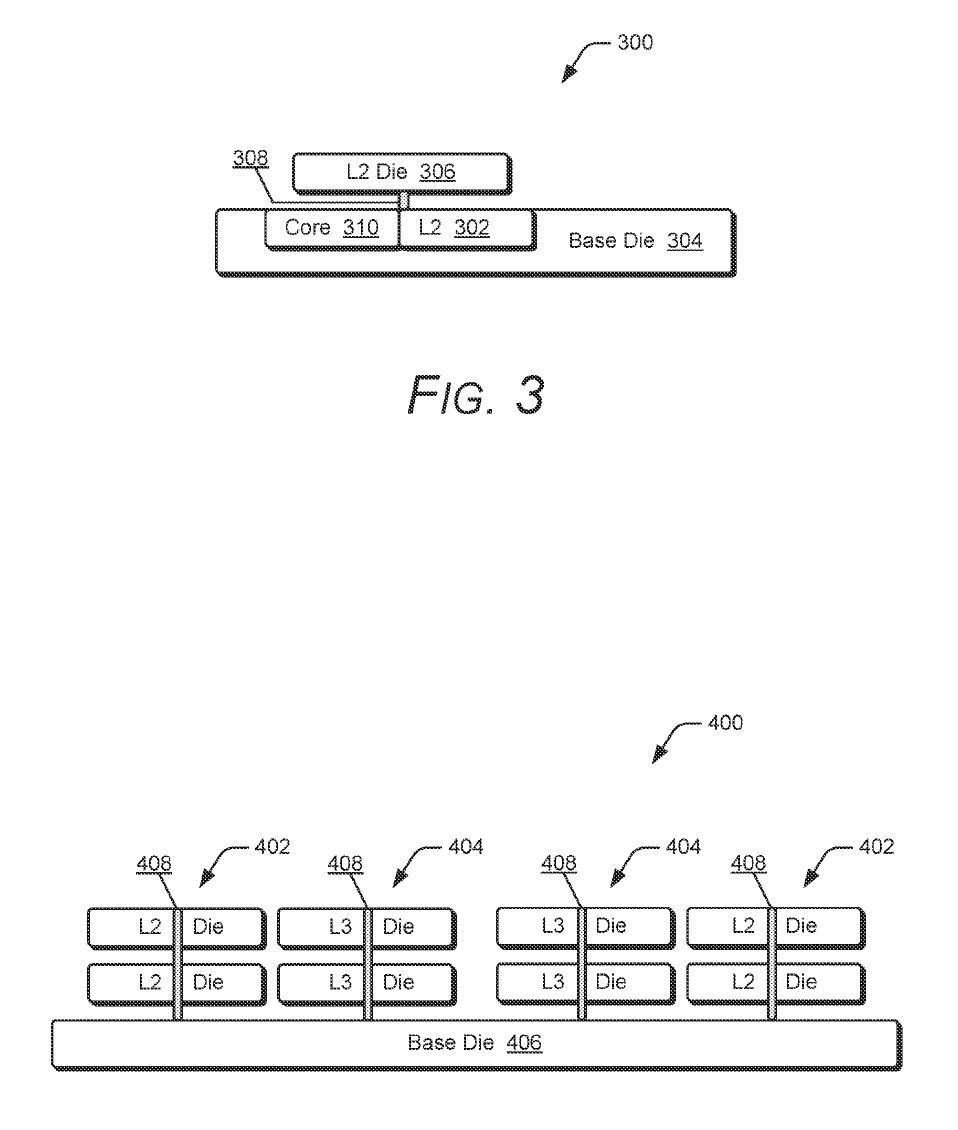

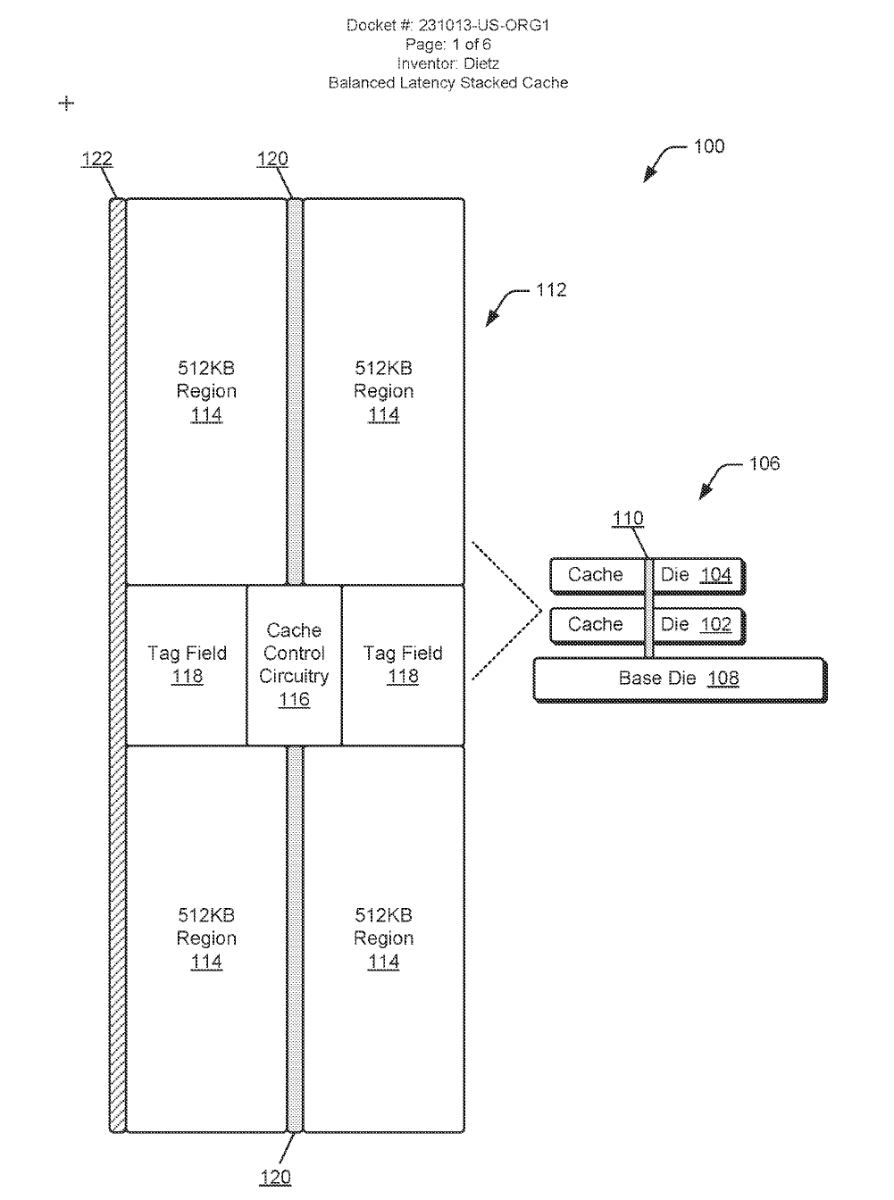

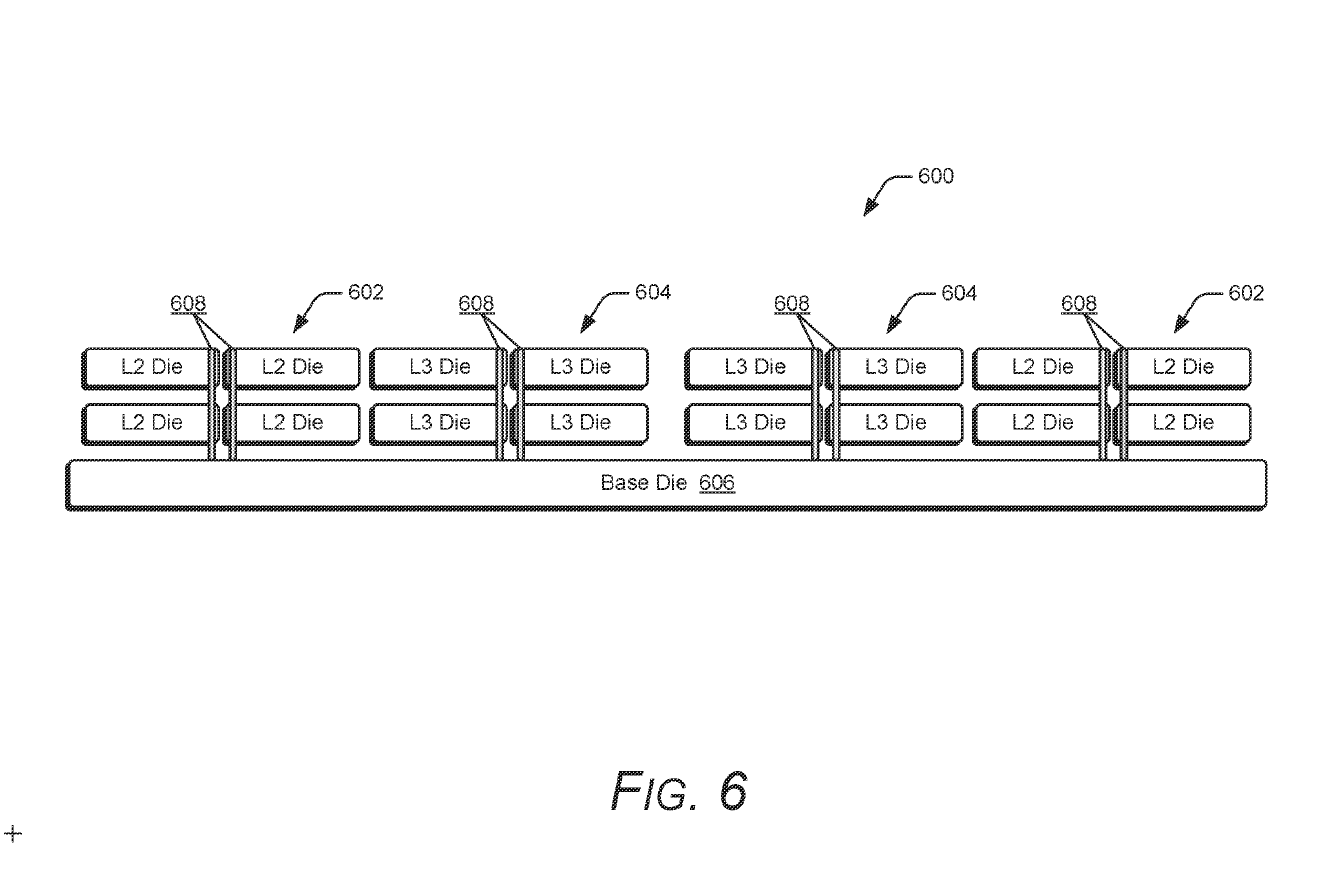

В патенте описывается следующая структура: основной кремниевый чип с основными вычислительными ядрами и стандартным уровнем L2-кэша дополняется дополнительным модулем с таким же уровнем памяти, который располагается непосредственно над первым слоем.

Например, в одном из примеров схемы используются четыре блока L2 по 512 килобайт каждый, что в сумме даёт 2 мегабайта кэша. Над этим стеком возможно размещение дополнительного модуля такого же объёма, удваивая доступный объём L2.

Помимо значительного увеличения объёма, AMD также отмечает снижение латентности. Компания утверждает, что задержка традиционного плоского двухуровневого кэша объёмом 1 мегабайт составляет около 14 тактовых циклов, в то время как предлагаемый трёхмерный вариант требует всего лишь 12 тактов, что повышает эффективность обработки запросов ядра.

Технология многоуровневой организации кэш-памяти должна позволить AMD создавать высокопроизводительные решения следующего поколения, обеспечивающие высокую пропускную способность и оптимизированные показатели энергопотребления.

Пока неизвестно, когда именно данная технология найдет свое применение в серийных продуктах компании. Однако сам факт регистрации патента свидетельствует о готовности производителя двигаться дальше в направлении оптимизации архитектуры CPU.