Организация PCI-SIG на этой неделе объявила, что спецификации PCIe 6.0 достигли статуса Final Draft, что является важной вехой, знаменующей завершение разработки стандарта. Все чипы, совместимые со спецификацией PCIe 6.0 версии 0.9, будут совместимы с последней версией 1.0.

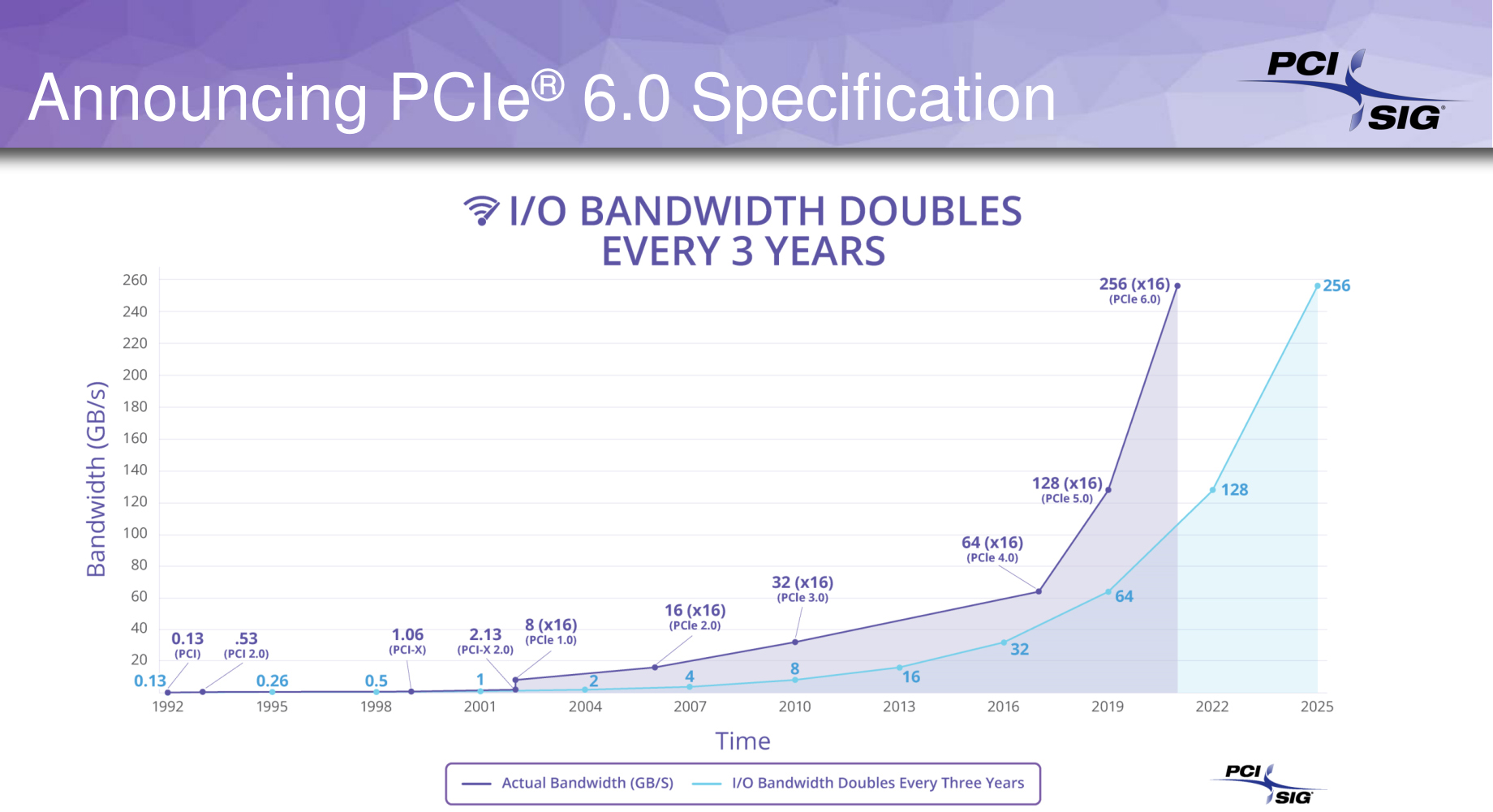

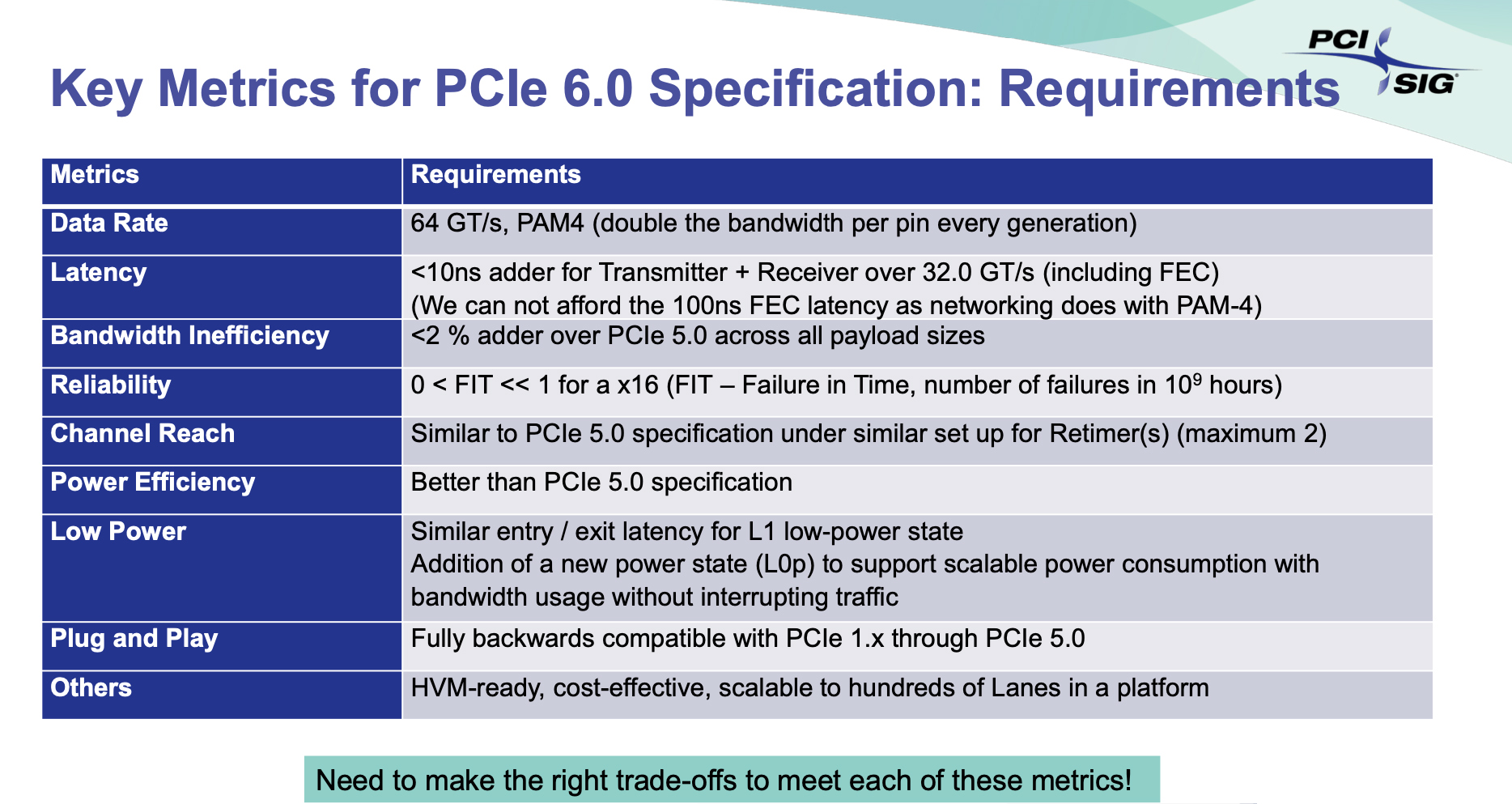

PCIe Gen6 увеличит скорость передачи данных до 64 ГТ/с на контакт, что в два и четыре раза больше соответственно 32 ГТ/с для PCIe Gen5 и 16 ГТ/с для PCIe Gen4. Новый стандарт сохранит обратную совместимость с существующим ныне оборудованием. Новая технология позволит передавать данные со скоростью до 128 ГБ в секунду в каждом направлении по интерфейсу x16.

Разработка спецификации PCI Express имеют пять основных этапов: концепция, первый проект, полный проект, окончательный проект и финал. Выпуск спецификации PCIe 6.0 Complete Draft (версия 0.7) чуть менее года назад позволил крупным компаниям и разработчикам, таким как Synopsys, начать создавать свои контроллеры PCIe 6.0. Публикация окончательных спецификации PCIe 6.0 (версия 0.9) знаменует собой точку, после которой никакие функциональные изменения уже не допускаются.

Те компании, которым удалось добавить поддержку PCIe 6.0 версии 0.9 в свои системы на кристалле (SoC), теоретически могут начать продавать их как PCIe 6.0 Ready, но они не смогут официально подтвердить соответствие окончательной версии PCIe 6.0 1.0, поскольку в настоящее время нет официальной программы соответствия PCIe 6.0.

Чтобы сделать возможными такие скорости передачи данных и пропускную способность, разработчики нового стандарта должны применять амплитудно-импульсную модуляцию с четырьмя уровнями (PAM-4) сигнализации, которая также используется для высокопроизводительных сетевых технологий, таких как InfiniBand, а также памяти GDDR6X. Кроме того, PCIe Gen6 поддерживает прямое исправление ошибок с малой задержкой (FEC) для обеспечения высокой эффективности при высоких скоростях передачи данных.

Хотя PCIe 6.0 является важным шагом в развитии интерфейса, он также создает многочисленные проблемы для разработчиков микросхем. Во-первых, PAM-4 дорог с точки зрения мощности и размера кристалла, поэтому он не получил широкого распространения, кроме стандартов 100GbE и 200GbE для центров обработки данных или сетевых стандартов корпоративного уровня. Во-вторых, 64 ГТ/с является очень высокой скоростью передачи данных, и хотя PAM-4 с FEC помогает устранить с некоторые трудности, передачу сигнала по печатным платам (PCB) необходимо оптимизировать для снижения перекрестных помех и потерь, отражений.

Это означает, что не все разработчики SoC будут стремиться добавлять поддержку PCIe 6.0 из-за проблем с ценой и энергопотреблением. Кроме того, реализация PCIe 6.0 на системном уровне потребует сложных печатных плат. Интерфейс PCIe 6.0 имеет смысл для серверов и специализированных систем, но может быть слишком дорогим для массового использования на начальном этапе развертывания.